不要低估一辆载满磁带飞奔的货车的带宽。

局部性原理

局部性原理表明了在任何时间内,程序访问的只是地址空间相对较小的一部分内容。

- 时间局部性: 如果某个数据被访问,那么在不久的将来他可能再次被访问

- 空间局部性: 如果某个数据被访问,与他地址相邻的数据可能很快被访问

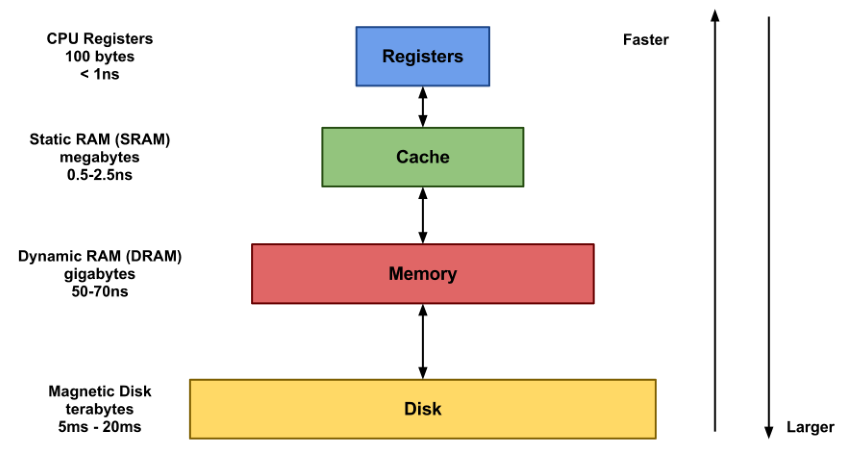

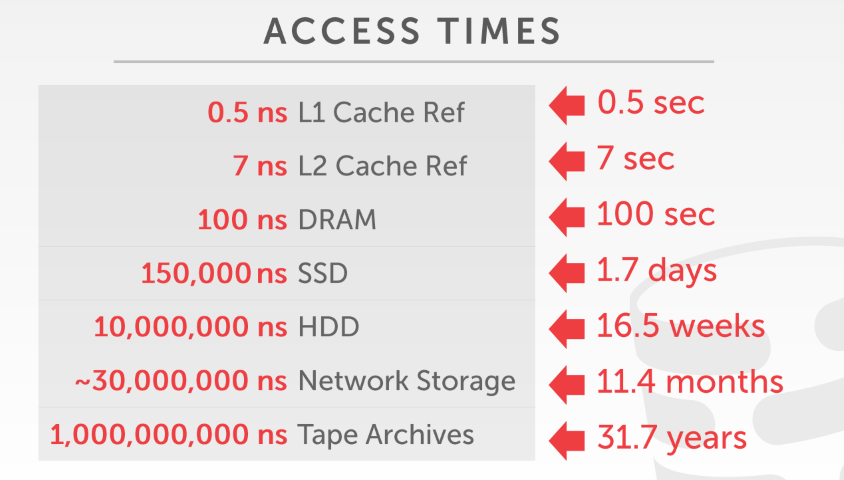

我们利用局部性原理将计算机存储器组织成为存储器层次结构(memory hierarchy)。存储器层次结构由不同速度和容量的多级存储器构成。

如果存储器需要的数据存放在高层存储器中的某个块中,则称为一次命中。命中率是在高层次存储器中找到数据的存储访问比例,是存储器层次结构性能的重要衡量指标。

存储器技术

目前,构建存储器层次结构主要有四种技术。

- 主存由 DRAM 实现

- cache 由 SRAM 实现

- 闪存非易失性存储器用作个人移动设备中的二级存储器

- 磁盘通常是服务器中容量最大速度最慢的一层

存储器的层次结构

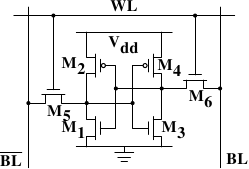

SRAM

上图是 6 晶体管 SRAM 的一个单元。核心是 4 个晶体管 M1-M4,它们组成两个交叉耦合的反相器。它们有两个稳定的状态,分别代表 0 和 1。

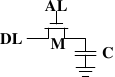

DRAM

动态 RAM 比静态 RAM 要简单得多。上图展示了一种普通 DRAM 的结构。它只含有一个晶体管和一个电容器。

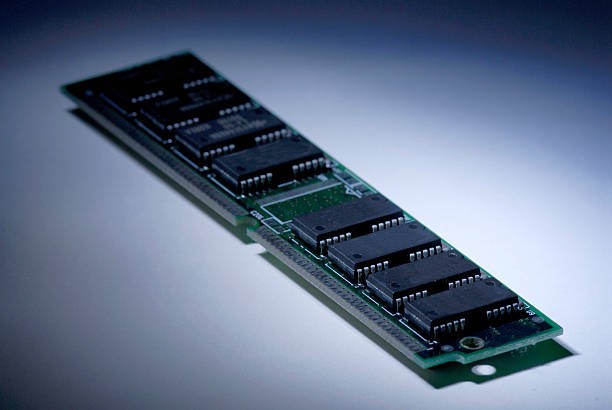

主存

上图就是一个内存模组(memory module),模组上面的一个个黑色芯片就是 DRAM 芯片。就构成了我们说的内存条。通常用于 PC 上,在移动设备上,内存通常集成于 SoC。

DDR

双倍数据传输率(Double Date Rate)严格的说 DDR 应该叫 DDR SDRAM,人们习惯称为 DDR。

DDR 内存是在 SDRAM 内存基础上发展而来的,仍然沿用 SDRAM 生产体系,因此对于内存厂商 而言,只需对制造普通 SDRAM 的设备稍加改进,即可实现 DDR 内存的生产,可有效的降低成本。

DDR 系统时脉为 100 或 133MHz,但是数据传输速率为系统时脉的两倍,即 200 或 266 MHz,系统使用 3.3 或 3.5V 的电压。因为 DDR SDRAM 的速度增加,因此它的传输效能比同步动态随机存取内存(SDRAM)好。SDRAM 在一个时钟周期内只传输一次数据,它是在时钟的上升期进行数据传输;而 DDR 内存则是一个时钟周期内传输两次次数据,它能够在时钟的上升期和下降期各传输一次数据,因此称为双倍速率同步动态随机存储器。DDR 内存可以在与 SDRAM 相同的总线频率下达到更高的数据传输率。

双通道

双通道(Dual-channel)是一种能够让电脑性能增加的技术,这种技术将多个内存由串联方式改良为并联方式,以得到更大的频宽。

高速缓存

Cache 对空间局部性的利用

- 从主存中取回带访问数据时,会同时取回与位置相邻的主存单元的数据

- 以块(Block)为单位和主存进行数据交换

Cache 对时间局部性的利用

- 保存近期被频繁访问的主存单元的数据。

Cache 的访问过程

- CPU 向 Cache 发出读请求

- 首先判断数据是否位于 Cache,若位于 Cache 中,则称为 Cache Hit,返回数据;若 Cache 中不存在,则称为 Cache Miss,并向主存发出读请求。(这一过程 CPU 不参与)

- 从主存中读取数据,更新 Cache 并返回数据

Cache 的写策略

- Cache 命中时的写策略

- 写穿透(Write Through): 数据同时写入 Cache 和主存

- 写返回(Write Back): 数据只写入 Cache,仅当该数据块被替换时才将数据写回主存

- Cache 失效时的写策略

- 写不分配(Write Non-Allocate): 直接将数据写入主存

- 写分配(Write Allocate): 将该数据所在的块读入 Cache 后,再将数据写入 Cache

少量对性能要求不高的系统采用写穿透-写不分配的策略,大多数都采用写返回-写分配的策略。

Cache 失效的原因

注意: 提高一点命中率,访存性能提升很高。

- 义务失效

第一次访问某一块数据,也成为冷启动(Cold Start Miss)。(无法避免) - 容量失效

Cache 无法保存程序访问所需的所有的数据块。(可通过过增加 Cache 容量解决) - 冲突失效

多个存储器位置映射到同一 Cache 位置。

Cache 映射策略

- 直接映射 Cache

- 组相联 Cache

Cache 替换算法

- 随机

- 轮转

- LRU

对于现在的多级高速缓存,如 Core I7,L1 Cache 会采用指令和数据分离的 Cache,L2 和 L3 则不分离。

存储容量的计算

单位前缀

- 高速缓存: 32KB = 32 x 1024Byte(K: 210,M: 220,G: 230)

- 内存: 4GB = 4 x 10243Byte

- U盘: 4GB = 4 x 10003Byte

- 硬盘: 1TB = 1 x 10004Byte

注意: 内部存储器使用 1024,而外部存储器使用 1000。